In den letzten Jahren wurden digitale Videoüberwachungssysteme in verschiedenen Bereichen wie Banken, Autobahnen und Gebäuden weit verbreitet eingesetzt. In digitalen Videoüberwachungssystemen ist die OSD-Technologie (On Screen Display) ein unverzichtbarer Bestandteil. OSD bietet Benutzern eine benutzerfreundliche Mensch-Maschine-Schnittstelle, über die Benutzer weitere zusätzliche Informationen erhalten können.

1. Systemzusammensetzung

Das in diesem Artikel vorgestellte System ist ein vollständiges Videoüberwachungssystem basierend auf TI DSP TMS320DM6? 3 und FPGA. Es unterstützt 1 Kanal Videoeingang und 1 Kanal Videoausgang und bietet außerdem eine Netzwerkschnittstelle.

Der Videoeingang wird durch den kostengünstigen Videodecoder TVP5150A von TI realisiert. TVP5150A kann die Sammlung von zwei Composite-Videoeingängen oder einem S-Video-Videosignal realisieren. Das Register wird über I2C konfiguriert und das ausgegebene digitale Videosignal folgt dem ITU656-Standard.

Das vom TVP5150A dekodierte digitale Videosignal wird über den Video-Port 1 des DM6 an den DSP übertragen? 3, und die erforderliche Videoverarbeitung wird vom DSP durchgeführt und dann über die Netzwerkschnittstelle an das Remote-Gerät ausgegeben. Andererseits nach DM6? 3 verarbeitet die vom Netzwerk empfangenen Videodaten, sie werden von SAA7105 über Videoport 2 über FPGA angezeigt und ausgegeben.

Der Ausgabeteil wird durch SAA7105 realisiert. SAA7105 ist ein Hochleistungs-Video-Encoder der NXP Company, der Composite-Video-Ausgang, VGA-Video-Ausgang und HDTV-High-Definition-Videosignal-Ausgang bieten kann. Die Steuerung des SAA7105 erfolgt ebenfalls über I2C und er empfängt das digitale Videosignal des Composite-ITU656-Standards.

Der Videoverarbeitungsteil wird mit dem DSP TMS320DM6 3 von TI realisiert. Die Hauptfrequenz des DM6?3 kann 600 MHz erreichen, und es gibt zwei 20-Bit-Videoanschlüsse. Die Videoanschlüsse unterstützen digitale Videoschnittstellen wie BT.656 und Y/C. DM6?3 integriert auch Netzwerk-MAC, um den Netzwerkzugriff zu realisieren.

Die Entwicklungsgeschwindigkeit der Hardwareleistung ist immer schwierig, den Anforderungen der Software gerecht zu werden. In den immer komplexer werdenden Anwendungen der Videoverarbeitung ist DSP für komplexe Videoverarbeitungsaufgaben verantwortlich und die Ressourcen werden sehr knapp. Daher wird beim Entwurf dieses Systems FPGA zur Realisierung des OSD-Designs verwendet, wodurch die Belastung des DSP verringert werden kann.

Der OSD-Implementierungsteil verwendet den XC3S250E von Xilinx. XC3S250E ist ein FPGA der SPARTAN-3E-Serie von Xilinx mit 250,000 Logikgattern.

2. OSD-Implementierung

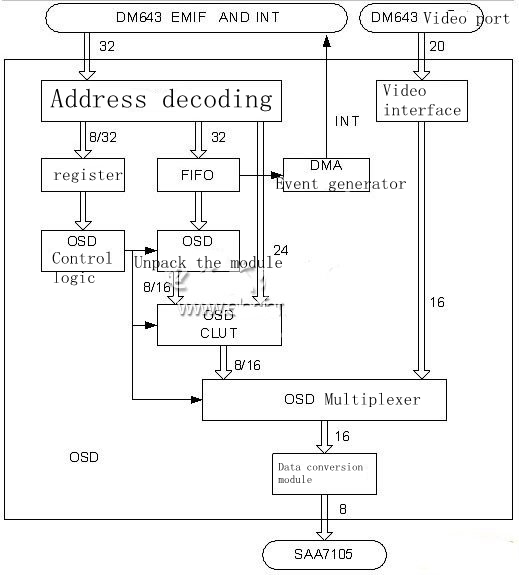

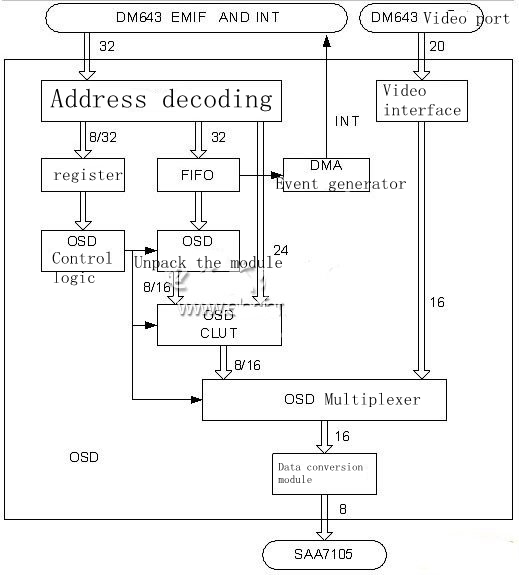

SAA7105 kann die OSD-Funktion nicht realisieren, wird aber von XC3S250E realisiert. Der Hauptsteuerchip DM6? 3 muss dem FPGA lediglich den anzuzeigenden Inhalt und die Position mitteilen, und die spezifische Arbeit wird vom FPGA ausgeführt. Das logische Blockdiagramm des OSD ist in Abb. 2 dargestellt.

OSD FPGA empfängt OSD-Daten und Steueranweisungen von DSP DM6 3 über EMIFA, empfängt Videodaten über DSP-Video-Port 1, überlagert OSD-Informationen mit den Videodaten und gibt sie an den Video-Encoder SAA7105 aus. Die Funktionsmodule von OSD werden wie folgt beschrieben.

Der Datenanschluss des Adressdekodierungsmoduls ist mit den niedrigen 32-Bit-Daten von EMIFA des DSP DM6 3 verbunden und empfängt die von DM6 3 gesendeten Daten und Steuerinformationen. Diese Daten und Steuerinformationen sind die ursprünglichen 32-Bit-Daten, die von DM6 3 gesendet wurden. Das Adressdekodierungsmodul legt die empfangenen OSD-Daten, wie z. B. den Inhalt des OSD, in einem 32-Bit-Datenformat im internen FIFO des FPGA ab. Die Steuerinformationen werden hauptsächlich zur Steuerung des OSD über einen Satz Steuerregister verwendet.

Es gibt auch ein Videoschnittstellenmodul, das direkt an den DSP angeschlossen ist. Das Videoschnittstellenmodul ist mit dem Video-Port 2 des DSP verbunden und speichert die Daten und Steuerinformationen vom DSP-Video-Port. Diese Steuerinformationen werden direkt an das OSD-Mehrkanal-Steuermodul übertragen, und die Steuerinformationen steuern auch direkt den Videodecoder SAA7105.

Die OSD-Steuerlogik gibt die von der Steuerregistergruppe erhaltenen Steuerinformationen an jedes Funktionsmodul des OSD aus, um die Steuerung des OSD zu realisieren. Die Registergruppe ist hauptsächlich in zwei Teile unterteilt: Der eine ist die asynchrone Registergruppe, die Steuerinformationen wie Zurücksetzen, OSD-Aktivierung und ausgewählte Datenbreite an das OSD sendet; Die andere ist die Synchronregistergruppe, die hauptsächlich die Positionsinformationen des OSD steuert.

Das OSD-Dekodierungsmodul entnimmt die anzuzeigenden Daten gemäß den Steuerinformationen der Steuerlogik aus dem FIFO und gibt sie synchron mit den Videodaten an das OSD CLUT-Modul aus. Die vom FIFO erhaltenen Daten sind die ursprünglichen 32-Bit-DSP-Daten, und die vom OSD CLUT-Modul benötigten Daten sind 8/16-Bit, sodass das OSD-Entpackmodul die 32-Bit-Daten entsprechend der Frequenz des Videoports entpacken muss. Die 32-Bit-Daten werden mit einer Breite von 8/16 an das OSD CLUT-Modul übertragen.

Eine weitere Funktion des FIFO-Moduls besteht darin, FIFO-Statusinformationen an das DMA-Ereignisgeneratormodul zu übertragen, z. B. FIFO voll oder FIFO leer. Der DMA-Ereignisgenerator überwacht diese Ereignisse und wenn sie auftreten, werden sie an DM6 gesendet? 3 in einem Interrupt-Modus, um korrekte Lese- und Schreibvorgänge im FIFO zu erreichen.

Das OSD-CLUT-Modul sucht nach dem entsprechenden Wert von YCbCr für die vom OSD-Entpackmodul empfangenen Daten jedes Pixels und steuert die Ausgabesequenz dieser OSD-CLUT-Daten. Diese Konvertierungsbeziehung wird vom DSP über den 24-Bit-Datenport übertragen. Die Daten des OSD CLUT-Moduls werden direkt an das OSD-Mehrkanal-Controller-Modul ausgegeben.

Das OSD-Mehrkanal-Steuermodul bestimmt die ausgegebenen Videodaten anhand des vom OSD-CLUT-Modul empfangenen Alpha-Steuerbits. Wenn die aktuellen OSD-Informationen, also das Alpha-Steuerbit, gültig sind, werden die OSD-Daten an das Datenkonvertierungsmodul ausgegeben. Andernfalls werden die vom Videoschnittstellenmodul empfangenen Originalvideodaten ausgegeben, um die OSD-Funktion zu realisieren.

Die vom OSD-Mehrkanalcontroller ausgegebenen Daten werden nicht direkt an den Videodecoder gesendet, sondern über das Datenkonvertierungsmodul wird entsprechend den spezifischen Anwendungsbedingungen die erforderliche Datenformatkonvertierung durchgeführt. Aus dem Schnittstellen-Timing von SAA7105 ist ersichtlich, dass es sich bei den erforderlichen Daten bei der Konfiguration des SAA7105 für die Composite-Video-Ausgabe um Einzeltaktflankendaten handelt. Zu diesem Zeitpunkt führt das Datenkonvertierungsmodul keine Arbeit aus und die vom OSD-Mehrkanal-Steuermodul empfangenen Daten werden intakt übertragen. Für SAA7105; Wenn SAA7105 im VGA- oder HDTV-Ausgabemodus konfiguriert ist, sind Dual-Clock-Edge-Daten erforderlich. Zu diesem Zeitpunkt wandelt das Datenkonvertierungsmodul die vom OSD-Controller empfangenen Einzeltaktflankendaten in Doppeltaktflankendaten um und gibt sie an den Videodecoder SAA7105 aus.

Es ist ersichtlich, dass FPGA die gesamte Arbeit des OSD abgeschlossen hat. Wenn Sie den OSD-Inhalt anzeigen möchten, DM6? 3 muss lediglich Steueranweisungen über den EMFIA-Port an das FPGA senden. Diese Anweisungen umfassen selbstverständlich die Inhalts- und Standortinformationen des OSD.

3. OSD-Steuerung

Das vom XC3S250E implementierte OSD-Design führt die OSD-Anzeige basierend auf den empfangenen OSD-Standort- und Inhaltsinformationen durch, ohne Einschränkungen für den vom OSD angezeigten Inhalt, was sehr flexibel und praktisch ist. Im Folgenden wird die Anzeige chinesischer Schriftzeichen im OSD als Beispiel zur Veranschaulichung der Steuerungsvorgänge des OSD verwendet.

Um chinesische Schriftzeichen korrekt anzuzeigen, muss der eingegebene interne Code für chinesische Schriftzeichen in den entsprechenden Standortcode umgewandelt werden. Für diese Funktion verwenden wir die Funktion Uint32 Code_Converse(unsigned char *CodeNPointer), deren Eingabe ein Zeiger ist, der auf das zu konvertierende chinesische Zeichen zeigt. Der Rückgabewert ist der Ortscode, der dem chinesischen Schriftzeichen entspricht. Die OSD-Anzeige wird durch die Funktion OSDHZ?isplay realisiert:

void OSDHZ_Display{

Uint8 *pFrame

Uint32-Pitch

OSDUTIL_Point* loc

Uint32 CodeQ

OSDHZ?ont *font

Uint8 fgColor

Uint8 bgColor

}

Unter diesen ist Uint8 *pFrame der Puffer für die OSD-Ausgabe; Der Uint32-Pitch ist der in jeder Zeile angezeigte Pixelwert. OSDUTIL_Point *loc ist die Anzeigeposition des ersten Zeichens; Uint32 CodeQ ist die Ortsvorwahl zur Anzeige chinesischer Schriftzeichen; OSDHZ?ont * Schriftart ist die Schriftart, die zur Anzeige chinesischer Schriftzeichen verwendet wird; Uint8 fgColor zeigt die Vordergrundfarbe chinesischer Schriftzeichen an; Uint8 bgColor zeigt die Hintergrundfarbe chinesischer Schriftzeichen an.

Wenn Sie also chinesische Schriftzeichen anzeigen müssen, müssen Sie nur die chinesischen Schriftzeichen in das erforderliche Codesystem konvertieren und dann die konvertierte Ortsvorwahl an das OSD-FPGA ausgeben. Um chinesische Schriftzeichen anzuzeigen, ist die chinesische Schriftzeichenbibliothek natürlich unverzichtbar.

Unsere anderen Produkt: